|

Глава 10. Цифровой логический уровень: организация памяти

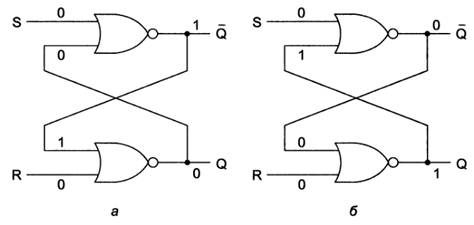

Защелки

Чтобы создать один бит

памяти, нужна схема, которая каким-то образом ««запоминает» предыдущие входные

значения. Такую схему можно сконструировать из двух вентилей НЕ-ИЛИ:

Рисунок 1 – SR-защелка НЕ-ИЛИ в состоянии 0 (а);

защелка НЕ-ИЛИ в состоянии 1 (б)

Аналогичные схемы можно

построить и из других вентилей.

У SR-защелки есть два

входа: S (Setting — установка) и R (Resetting — сброс), а также есть два

комплиментарных выхода: Q и

. В отличие от комбинаторной схемы, выходные сигналы защелки

не определяются текущими входными сигналами. . В отличие от комбинаторной схемы, выходные сигналы защелки

не определяются текущими входными сигналами.

Предположим, что S = 0 и R

= 0 (вообще сигнал на этих входах равен 0 большую часть времени). Предположим

также, что Q=0. Так как Q возвращается в верхний вентиль НЕ-ИЛИ и оба входа

этого вентиля равны 0, то его выход,

, равен 1. Единица возвращается в нижний вентиль, у которого в

итоге один вход равен 0, другой — 1, а на выходе получается

Q

= 0. Такое положение вещей

состоятельно . , равен 1. Единица возвращается в нижний вентиль, у которого в

итоге один вход равен 0, другой — 1, а на выходе получается

Q

= 0. Такое положение вещей

состоятельно .

Другая ситуация:

Q

= 1,

a

R=0

и

S=0 . Верхний вентиль имеет входы 0 и 1 и

выход

(то есть 0), который

возвращается в нижний вентиль. Такое положение вещей также состоятельно. (то есть 0), который

возвращается в нижний вентиль. Такое положение вещей также состоятельно.

Положение, когда оба выхода

равны 0, не состоятельно, поскольку в этом случае оба вентиля имели бы на входе

два нуля, что привело бы к единице на выходе, а не к нулю. Точно так же

невозможно иметь оба выхода равные 1, поскольку это привело бы к входным

сигналам 0 и 1, что вызывает на выходе 0, а не 1.

Вывод: при

R

=

S = 0 защелка имеет два устойчивых

состояния, которые обозначим 0 и 1 в зависимости от

Q.

Рассмотрим действие входных

сигналов на состояние

SR-защелки.

Предположим,

S

принимает значение 1, в то время как

Q

= 0. Тогда входные сигналы верхнего вентиля равны 1 и 0, что ведет к выходному

сигналу

=0. Это изменение делает оба входа в нижний вентиль равными 0,

и, следовательно, выходной сигнал равняется 1. Таким образом, установка

S

в значение 1 переключает состояние с 0 на 1. Установка

R

в значение 1, когда защелка находится в состоянии 0, не вызывает изменений,

поскольку выход нижнего вентиля НЕ-ИЛИ равен 0 как для входов 10, так и для

входов 11. =0. Это изменение делает оба входа в нижний вентиль равными 0,

и, следовательно, выходной сигнал равняется 1. Таким образом, установка

S

в значение 1 переключает состояние с 0 на 1. Установка

R

в значение 1, когда защелка находится в состоянии 0, не вызывает изменений,

поскольку выход нижнего вентиля НЕ-ИЛИ равен 0 как для входов 10, так и для

входов 11.

Следовательно, установка

S

в значение 1 при состоянии защелки 1 (Q=1) не вызывает изменений, но установка R

в значение 1 приводит к изменению состояния защелки. Таким образом, если S

принимает значение 1, то Q равняется 1 независимо от предыдущего состояния

защелки. Сходным образом переход R в значение 1 вызывает Q = 0.

Вывод: схема «запоминает»,

какой сигнал был последним: S или R. Используя это свойство, можно строить

компьютерную память.

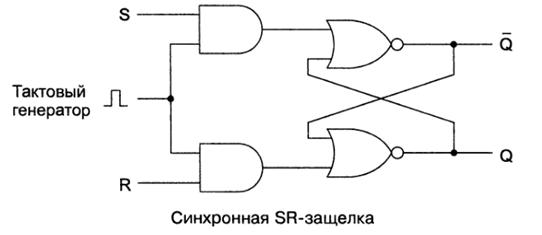

Синхронные SR-защелки

Часто удобно, чтобы защелка

меняла состояние только в определенные моменты времени. Чтобы достичь этой цели,

необходимо изменить основную схему и в результате получим синхронную SR-защелку:

Данная схема имеет

дополнительный синхронизирующий вход, который по большей части равен 0.

Если вход равен 0, то оба

выхода вентилей И равны 0, и независимо от значений S и R защелка не меняет свое

состояние. Когда значение синхронизирующего входа равно 1, действие вентилей И

прекращается, и состояние защелки становится зависимым от S и R.

Для обозначения факта

появления единицы на синхронизирующем входе часто используются термины включение

и стробирование.

Предположим, S = R = 1.

Единственное приемлемое состояние

при S = R = 1 - это Q =

= 0, но как только оба

входа возвращаются к 0, защелка должна перейти в одно из двух устойчивых

состояний. Если один из входов принимает значение 0 раньше, чем другой,

оставшийся в состоянии 1 «побеждает», потому что именно единичный вход управляет

состоянием защелки. Если оба входа переходят к 0 одновременно (что очень

маловероятно), защелка выбирает одно из своих устойчивых состояний произвольным

образом. = 0, но как только оба

входа возвращаются к 0, защелка должна перейти в одно из двух устойчивых

состояний. Если один из входов принимает значение 0 раньше, чем другой,

оставшийся в состоянии 1 «побеждает», потому что именно единичный вход управляет

состоянием защелки. Если оба входа переходят к 0 одновременно (что очень

маловероятно), защелка выбирает одно из своих устойчивых состояний произвольным

образом.

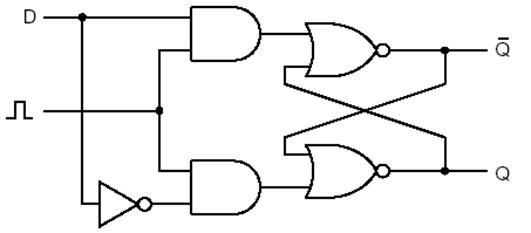

Синхронные D-защелки

Чтобы разрешить ситуацию с

неопределенностью SR-защелки в случае, если S = R= 1, нужно не дать ей

возникнуть. На рисунке изображена схема защелки только с одним входом D.

Так как входной сигнал в

нижний вентиль И всегда является обратным кодом входного сигнала в

верхний вентиль И, ситуация, когда оба входа равны 1, никогда не возникает.

Когда D = 1 и

синхронизирующий вход равен 1, защелка переходит в состояние Q = 1.

Когда D = 0 и

синхронизирующий вход равен 1, защелка переходит в состояние Q = 0.

В результате, когда

синхронизирующий вход равен 1, текущее значение D отбирается и сохраняется в

защелке. Такая схема называется синхронной D-защелкой и представляет собой

память объемом 1 бит. Сохраненное значение всегда доступно на выходе Q. Чтобы

загрузить в память текущее значение

D

нужно пустить положительный импульс по линии синхронизирующего сигнала.

Такая схема требует 11

транзисторов для хранения 1 бит памяти.

Триггеры

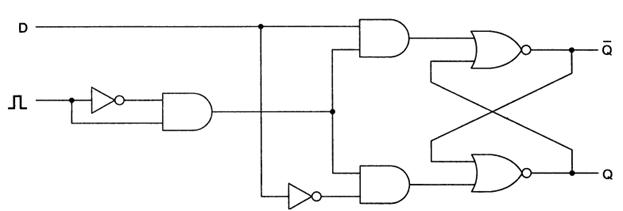

В схеме триггер смена

состояния происходит при переходе синхронизирующего сигнала с 0 на 1 (фронт) или

с 1 на 0 (спад). При этом длина синхронизирующего импульса не имеет значения,

поскольку переходы происходят быстро.

Различие между триггером и

защелкой:

-

триггер

запускается перепадом сигнала

-

защелка

запускается уровнем сигнала.

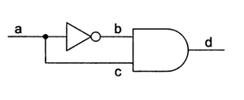

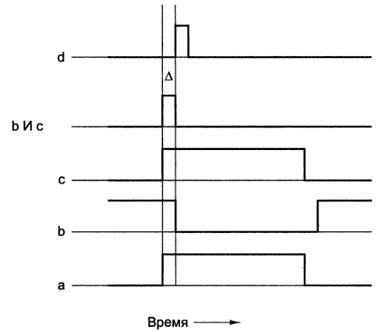

На рисунке представлена

схема генерирования очень короткого импульса на фронте синхронизирующего

сигнала.

Этот импульс можно подавать

в D-защелку.

При прохождении сигнала

через инвертор происходит небольшая, ненулевая задержка. Данная схема работает

именно благодаря этой задержке.

Предположим, что мы

измеряем напряжение в четырех точках:

a,

b,

c

и d. Входной сигнал в точке

a

представляет собой длинный синхронизирующий импульс. Сигнал в точке

b показан над ним. Отметим, что этот

сигнал инвертирован и подается с некоторой задержкой. Время задержки зависит от

типа инвертора и обычно составляет несколько наносекунд.

Сигнал в точке

с тоже подается с задержкой, но эта

задержка обусловлена только временем прохождения сигнала (со скоростью света).

Если физическое расстояние между точками

а и с составляет, например,

20 мкм, тогда задержка на распространение сигнала равна 0,0001 нс. Таким

образом, сигнал в точке с

практически идентичен сигналу в точке а.

Когда входные сигналы

b и

с подвергаются операции И, в

результате получается короткий импульс, длина которого (D)

равна вентильной задержке инвертора (обычно 5 нс и ниже). Выходной сигнал

вентиля И — данный импульс, сдвинутый из-за задержки вентиля И. Этот временной

сдвиг означает только то, что D-защелка активизируется с определенной задержкой

после фронта синхронизирующего импульса. Он никак не влияет

на длину импульса.

Рисунок 2 –

временная диаграмма для четырех точек

В памяти со временем цикла

в 50 нс импульс в 5 нс (который сообщает, когда нужно выбирать линию D)

достаточно короткий. Следует упомянуть, что такая схема триггера проста для

понимания, но на практике обычно используются более сложные триггеры (например,

D-триггер).

Рисунок

3 - D-триггер

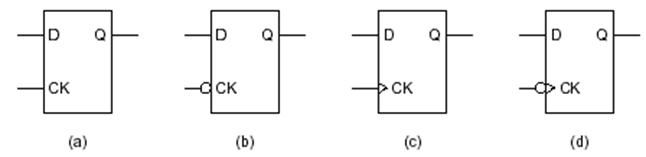

Стандартные обозначения

защелок и триггеров показаны на рисунке:

Рисунок

4

- D-защелки

и

D-триггеры

(a) - защелка, состояние

которой загружается тогда, когда синхронизирующий сигнал СК (clock)

равен 1.

(b)

- защелка, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0,

чтобы загрузить состояние из линии D.

(c)

– триггер, изменяет состояние на фронте синхронизирующего импульса (переход от 0

к 1)

(d)

– триггеры, изменяет состояние на спаде (переход от 0 к 1).

Защелки и триггеры также

имеют выход Q, а у некоторых есть два дополнительных входа: Set (установка) или

Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый

вход (Set или Preset) устанавливает Q = 1, а второй (Reset или Clear) — Q = 0.

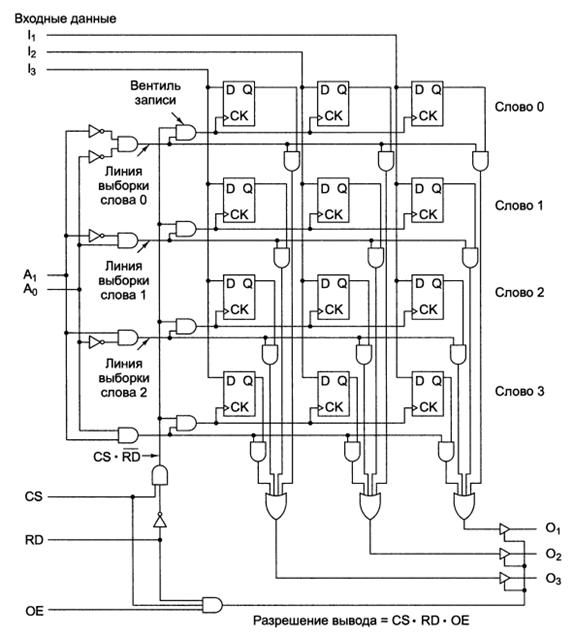

Организация памяти

Пример организации памяти,

которая содержит четыре 3-разрядных слова. Каждая операция считывает или

записывает целое 3-разрядное слово. Общий объем памяти -12 бит.

Рисунок 5 - Логическая блок-схема для памяти 4x3. Каждый ряд представляет одно из

3-разрядных слов. При считывании и записи всегда считывается

или записывается целое слово

Организация памяти очень

проста благодаря своей регулярной структуре. Микросхема содержит 8 входных

линий, в частности 3 входа для данных —

, ,

и и

; 2 входа для адресов — ; 2 входа для адресов —

и и

; 3 входа для управления — CS (Chip Select — выбор элемента

памяти), RD (ReaD — чтение, этот сигнал позволяет отличать считывание от записи)

и ОЕ (Output Enable — разрешение выдачи выходных сигналов), а также 3 выходные

линии для данных — ; 3 входа для управления — CS (Chip Select — выбор элемента

памяти), RD (ReaD — чтение, этот сигнал позволяет отличать считывание от записи)

и ОЕ (Output Enable — разрешение выдачи выходных сигналов), а также 3 выходные

линии для данных —

, ,

и и

. Такую память в принципе можно поместить в корпус с 14

выводами (включая питание и землю). . Такую память в принципе можно поместить в корпус с 14

выводами (включая питание и землю).

Чтобы выбрать микросхему

памяти, внешняя логика должна установить сигнал CS в 1, а также установить

сигнал RD в 1 для чтения и в 0 для записи. Две адресные линии должны указывать,

какое из четырех 3- разрядных слов нужно считывать или записывать. При

считывании входные линии для данных не используются. Выбирается слово и

помещается на выходные линии для данных. При записи биты, находящиеся на входных

линиях для данных, загружаются в выбранное слово памяти; выходные линии при этом

не используются.

Работа памяти (запись):

1.

Четыре вентиля И

для выбора слов в левой части схемы формируют декодер.

2.

Входные инверторы

расположены так, что каждый вентиль запускается определенным адресом.

3.

Каждый вентиль

приводит в действие линию выбора слов (для слов 0, 1, 2 и 3).

4.

Когда микросхема

должна производить запись, вертикальная линия CS-RD получает значение 1,

запуская один из четырех вентилей записи.

5.

Выбор вентиля

зависит от того, какая именно линия выбора слов равна 1.

6.

Выходной сигнал

вентиля записи приводит в действие все сигналы СК для выбранного слова, загружая

входные данные в триггеры для этого слова. Запись производится только в том

случае, если сигнал CS равен 1, a RD — 0, при этом записывается только слово,

выбранное адресами

и и

, остальные слова не меняются. , остальные слова не меняются.

Работа памяти (считывание):

1.

Декодирование

адреса происходит точно так же, как и при записи. Но в данном случае линия CS-RD

принимает значение 0, поэтому все вентили записи блокируются, и ни один из

триггеров не меняется.

2.

Вместо этого

линия выбора слов запускает вентили И, связанные с битами Q выбранного слова.

3.

Выбранное слово

передает свои данные в 4-входовые вентили ИЛИ, расположенные в нижней части

схемы, а остальные три слова выдают 0. Следовательно, выход вентилей ИЛИ

идентичен значению, сохраненному в данном слове.

4.

Остальные три

слова никак не влияют на выходные данные.

|